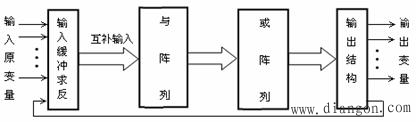

典型的PLD由一个“与”阵列和一个“或”阵列组成,而任意一个组合逻辑都可以用“与-或”表达式来描述,所以简单PLD能以乘积和的形式完成大量的组合逻辑功能。

图1 PLD结构框图

1. PLD的表示方法

PLD电路由与阵列和或阵列组成。连线交叉点“ x ”表示与门的一个输入端与一个外输入相连接,或门阵列的几列连线交叉点“﹒”表示一个或门可以和几个与门输出端相连接。 通过编程使可编程连接单元的某些点连接,某些点断开。下图中 构成了同或门, 构成了异或门。

图2 PLD表示法示意图

2. 可编程阵列逻辑器件(PAL)

它是由可编程的与门阵列和固定连接的或门阵列以及其它附加的输出电路组成,或门的输出可以通过触发器有选择地被置为寄存状态。在尚未编程前,与逻辑阵列所有的交叉点均有快速熔丝连通。编程时将有用的熔丝保留,无用的熔丝熔断,就得到所需的电路。用户可根据使用需要,选择其阵列结构大小、输入/输出的方式,以实现所需的各种组合逻辑功能和时序逻辑功能。

3. 可编程通用逻辑器件(GAL)

它继承了PAL器件的与或阵列结构,但在结构和工艺上作了很大改进。PAL器件采用双极性熔丝工艺,一旦编程就不能改写,这给用户修改电路带来不便。可编程通用逻辑器件GAL采用了E2PROM工艺,实现了电可擦除、电可改写,具有低功耗、电擦除可反复编程、速度快的特点,其输出结构是可编程的逻辑宏单元,通过编程可将输出逻辑宏单元(Output Logic Macro Cell,OLMC)设置成不同的工作状态,从而增加了器件的通用性。

GAL按门阵列的可编程结构可分为两大类:一类是与PAL基本结构相类似的普通型GAL器件,其与门阵列是可编程,或门阵列固定连接,这类器件如20引脚的GAL16V8;另一类是与门阵列和或门阵列均可编程,如24引脚的GAL39V8。