AT89S52单片机I/O端口有串行和并行之分,有P0、P1、P2和P3四个8位并行I/O端口,共占32根引脚,每一个I/O端口都能独立地用作输入或输出;有1个串行I/O端口,一次只能传送一位二进制信息。

1.并行I/O端口

P0口为三态双向口,P1、P2、P3口为准双向口。

(1)P0端口

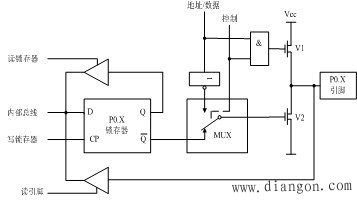

P0口字节地址80H,位地址80H~87H。P0口除作为准双向通用I/O接口使用外,还有更重要的两种功能:分时复用为地址总线和数据总线。P0口输出时能驱动8个LSTTL负载,即输出电流不小于800μA。P0口位结构如图1所示。

图1 P0口位结构 当P0口用作输出口使用时,在驱动NMOS电路时应外接上拉电阻;输入操作有读引脚和读锁存器之分。

(2)P1端口

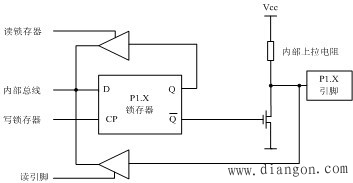

P1口字节地址90H,位地址90H~97H。P1口只有作为通用输入/输出接口的功能。P0口位结构如图2所示。

图2 P1口位结构 AT89S52的P1.0和P1.1是多功能引脚,P1.0可作定时器/计数器2的外部计数触发输入端T2,P1.1可作定时器/计数器2的外部控制输入端T2EX。

(3)P2端口

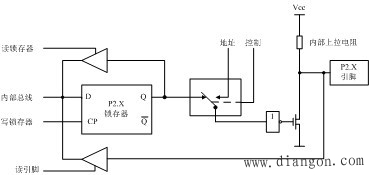

P2口字节地址A0H,位地址A0H~A7H。P2口是一个8位准双向I/O口,具有两种功能。一是作通用I/O口用,与P1口相同。二是作系统扩展外部存储器的高8位地址总线,输出高8位地址,与P0口一起组成16位地址总线。P2口位结构如图3所示,

图3 P2口位结构 (4)P3端口

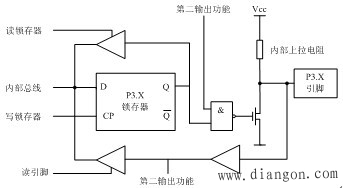

P3口字节地址B0H,位地址B0H~B7H。P3口也是一个8位准双向I/O口,既可以字节操作,也可以位操作;既可以8位口操作,也可以逐位定义口线为输入线或输出线;既可以读引脚,也可以读锁存器,实现“读一修改一输出”操作。P3口的位结构如图4。

图4 P3口位结构

P3口除具有与P1口同样的功能外,还具有第二功能,如表1所示

表1 P3口的第二功能 2.串行I/O端口

AT89S52有一个全双工的可编程串行I/O端口。这个串行I/O端口既可以在程序控制下将CPU的8位并行数据变成串行数据一位一位地从发送数据线TXD发送出去,也可以把串行接收到的数据变成八位并行数据送给CPU,而且这种串行发送和串行接收可以单独进行,也可以同时进行。

AT89S52串行发送和串行接收利用了P3口的第二功能,即利用P3.1 引脚作为串行数据的发送线TXD和P3.0引脚作为串行数据的接收线RXD。