本文探讨在微波暗室一致性测试之前构建低电磁干扰(EMI)原型的关键步骤,包括设计低辐射的电路以及预兼容检测。预兼容检测包括使用三维电磁场仿真软件对印刷电路板(PCB)版图模型进行仿真及EMI分析,再使用频谱分析仪(SA)对原型PCB进行近场电磁扫描。最后,执行微波暗室测试验证设计。

最低EMI电路设计

要确保低辐射发射(RE),设计电路原理图和PCB版图时必须应用最佳实践经验,包括为供电回路、USB数据线、以太网等信号添加铁氧体磁珠以过滤EMI.此外,供电回路上适当放置充足数量的去耦合电容器可以最大限度地减少电源分配网络阻抗,进而降低数字负载产生的噪声纹波幅度,并减少辐射风险。同时,优化开关电源的闭合回路补偿网络设计以实现稳定闭合回路,能够确保电压输出可控,并最大幅度地降低开关噪声纹波幅度。噪声纹波幅度降低可以显着抑制原型的EMI风险。

高频或快上升/下降沿信号的PCB走线应参考连续回路(例如参考地平面),以降EMI风险。走线不能经过任何分割平面和孔洞。如果信号需要通过过孔完成层间传输,紧邻信号过孔位置应放置至少一个接地过孔,作为信号电流从接收端返回发射端的回流路径。如果没有适当的回流路径,返回电流可能在PCB中随意传输,成为潜在的EMI源。

出色的接地方案也是最大限度降低EMI的关键因素。所有PCB设计都必须避免接地回路,因为返回信号电流经过时接地回路将形成辐射发射机。设计接地为宽参考面可以构建出色的接地方案。不同电路组(例如射频、模拟和数字电路)的地平面应当物理隔离,并通过铁氧体磁珠建立电路连接,以帮助防止高频噪声在电路组之间传播。

完成PCB版图设计后应执行仿真进行EMI分析,以便在制造前确保PCB具有较低的辐射发射风险。省略EMI仿真可能无法保证PCB的EMI性能,会导致重新设计。如果EMI仿真结果符合技术规范要求,设计人员即可开始PCB制造,然后使用频谱分析仪对原型PCB执行近场电磁扫描。EMI仿真和近场电磁扫描等预兼容检测可以增加设计人员的信心,确信原型具有较低的EMI.完成预兼容检测后,被测器件即可执行实际微波暗室EMI一致性测试。

仿真EMI分析

完成PCB版图设计后,将版图文件导入EMPro 2013.07 执行3D EMI仿真。选择差分信号进行有限元法(FEM)三维电磁场仿真。三维电磁场仿真是设置电磁边界条件和模型网格尺寸并求解麦克斯韦方程的过程。为确保仿真结果精度,边界尺寸应设为 PCB厚度的8倍以上,网格尺寸应设为PCB宽度的1/5以下。运行三维电磁场的计算机需要配置16G以上的内存和100G以上的存储容量,以确保分析顺利进行。

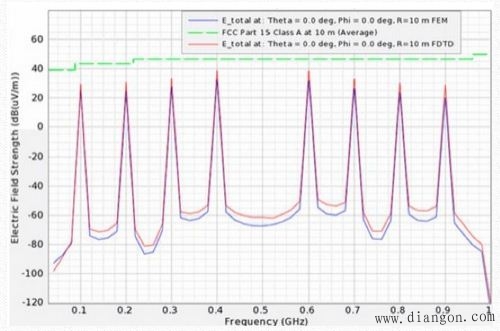

设置远场传感器捕获发射电磁场,并利用EMPro的EMI仿真模版计算远场发射功率,然后设置10m距离的电场探头,绘制频域响应图。再执行时域有限差分法(FDTD)模式的三维电磁场仿真,并与FEM模式的仿真结果进行对比。

参见30MHz~1GHz频率的电场强度仿真图(图1)(电场强度单位dBμV,频率单位GHz),辐射功率电平(蓝色曲线为FEM模式仿真,红色曲线为FDTD模式仿真)低于约45dBμV的FCC最大阈值(绿色虚线)。

图1:仿真EMI图。

近场电磁测量

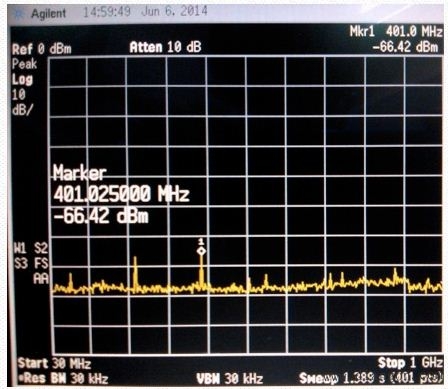

制成并组装原型PCB后,使用频谱分析仪对原型进行近场电磁扫描。连接频谱分析仪的单匝线圈捕获原型发射的近区电磁场。图2是30MHz~1GHz频率范围的频域信号(电磁场功率电平单位dB,频率单位Hz)。

图2:电磁扫描测量图。

400MHz附近时出现最大功率强度(-66.4dBm)的尖峰。作为近区传感器的线圈在距离被测器件3英寸的范围内移动。30kHz的频谱分析仪分辨率带宽可以实现低本底噪声(-80dBm)测量,因此尖峰(不同离散频率的辐射)清晰可见。要增强原型通过微波暗室远场(3m和10m)EMI一致性测试的信心,近区功率峰值应低于-65dBm。

EMI一致性测试

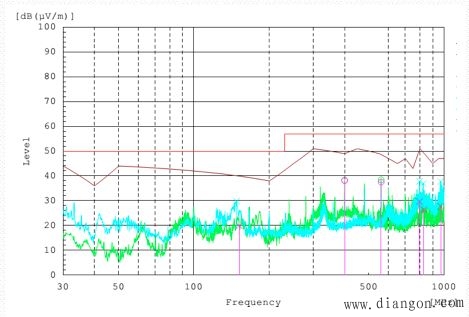

图3为原型在微波暗室的3m远场EMI一致性测试结果。红线显示的是CISPR 11 A类最大辐射发射功率电平:30MHz~1GHz频率范围内低于56dBμV。红线下方的棕色曲线表示是德科技(原安捷伦)EMC指南中规定的保护频段。辐射波的垂直和水平分量分别由蓝色和绿色曲线表示。400MHz和560MHz频率时出现两个分别为38dBμV 和37 dBμV的功率峰值,均低于最大阈值。

图3:3m辐射发射测量结果。

总结

低EMI电路设计和预兼容检测(例如三维EMI仿真和近场电磁扫描)十分重要,可以避免不必要的PCB重新制造,节省开发成本和时间,并且能够缩短微波暗室EMI一致性测试时间,确保电子器件按时甚至提前投放市场。