1.8线—3线优先编码器74148

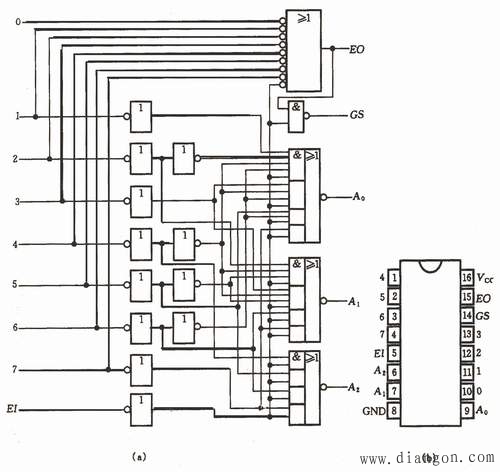

优先编码器74148的逻辑图和引脚图分别如图1(a)和1(b)所示,其功能如表1所示

图1 优先编码器74148的逻辑图和引脚图(a)逻辑图(b)引脚图

该编码器有8个信号输入端,3个二进制码输出端。此外,电路还设置了输入使能端EI,输出使能端EO和优先编码工作状态标志GS。 当EI=0时,编码器工作;当EI=1时,则不论8个输入端为何种状态,3个输出端均为高电平,且优先标志端和输出使能端均为高电平,编码器处于非工作状态。这种情况被称为输入低电平有效,输出也有低电平有效的情况。当EI为0,且至少有一个输入端有编码请求信号(逻辑0)时,优先编码工作状态标志GS为0,表明编码处于工作状态,否则为1。由功能表可知,在8个输入端均无低电平输入信号和只有输入0端(优先级别最低位) 有低电平输入时,A2A1A0均为111,出现了输入条件不同输出代码相同的情况,这可由GS的状态加以区别,GS=1时,表示8个输入端均为无低电平输入,此时A2A1A0=111为非编码输出;GS=0时,A2A1A0=111表示响应输入0的输出代码,A2A1A0=111可编码输出。EO只有在EI为0,且所有输入端都为1时,输出为0,它可与另一片同样器件的EI连接,以便组成更多输入端的优先编码器。

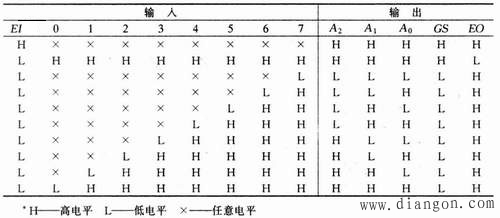

| 表1 优先编码器74148功能表 |

(这里不采用对变量符号加非号的方式表示低电平有效,防止会引起与其他非号的混淆。) |

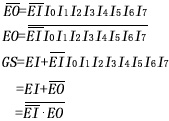

为了能够列出逻辑表达式,我们设输入0,1,…,7对应的变量为I0,I1,…,I7,根据功能表,写出各输出端的逻辑表达式。

|

|

|

经过变换得

同理可得输出A1和A0的表达式如下:

|

|

|

|

下面通过举例来了解74148的应用。

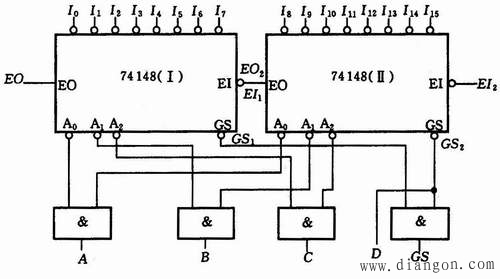

例1用两片74148组成16位输入、4位二进制码输出的优先编码器,逻辑图如下图所示,试分析其工作原理。

|

| 图2 例5.2.1的逻辑图 |

(1)当EI2=1时,EO2=1,从而使EI1=1,这时74148(I)(II)均禁止编码,它们的输出端A2A1A0都是111。由电路图可知,GS=GS1·GS2=1,表示此时整个电路的代码输出端DCBA=1111是非编码输出。

(2)当EI2=0时,高位片(II)允许编码,但若I15~I8都是高电平,即均无编码请求,则EO2=0,从而EI1=0,允许低位片(I)编码。这时高位片的A2A1A0=111,使门C、B、A都打开,C、B、A取决于低位片的A2A1A0,而D=GS2,总是等于1,所以输出代码在1111~1000之间变化。如果I0单独有效,输出为1111;如果I7及任意其他输入同时有效,则输出为1000,低位片以I7的优先级别最高。

(3)当EI2=0且I15~I8中有编码请求(至少一个为低电平)时,EO2=1,从而EI1=1,高位片编码,低位片禁止编码。显然,高位片的编码级别优先于低位片。此时D=GS2=0,C、B、A取决于高位片的A2A1A0,输出代码在0111~0000之间变化,同理可知,高位片中的I15的优先级别最高。整个电路实现了16位输入的优先编码,其中I15具有最高的优先级别,优先级别从I15至I0依次递减。

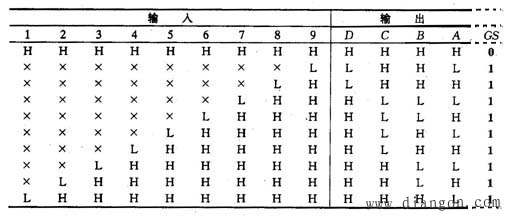

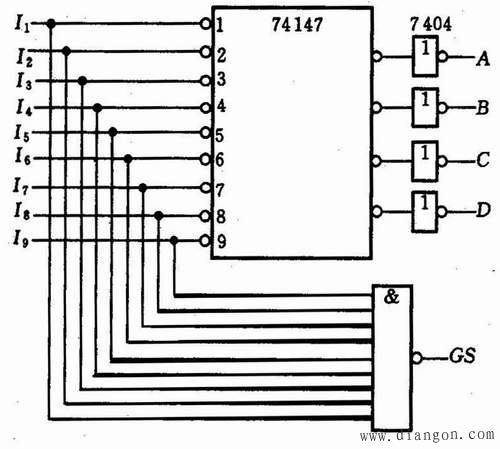

例2 优先编码器74147的功能如表2(实线部分)所示,试用74147和适当的门构成输出为8421BCD码并具有编码输出标志的编码器。

| 表2 例2表 |

|

|

| 图3 例2 的逻辑图 |

综上所述,对编码器归纳为以下几点:

1.编码器的输入端子数N(要进行编码的信息的个数)与输出端子数n(所得编码的位数)之间应满足关系式N≤2n。

2.编码器的每个输入端都代表一个二进制数、十进制数或其它信息符号,而且在N个输入端中每次只允许有一个输入端输入信号(输入低电平有效或输入高电平有效),输出为相应的二进制代码或二-十进制代码(BCD码)。

3.正确使用编码器的控制端,可以用来扩展编码器的功能。