1.用SSI器件设计时序逻辑电路

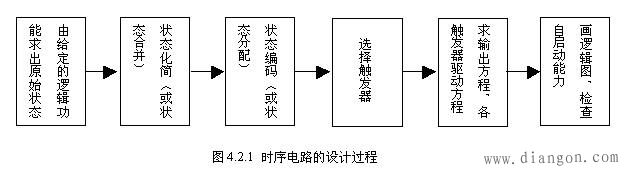

用触发器及门电路设计时序逻辑电路的一般步骤如图所示。

(1)由给定的逻辑功能求出原始状态图:首先分析给定的逻辑功能,从而求出对应的状态转换图。这种直接由要求实现的逻辑功能求得的状态转换图叫做原始状态图。

(2)状态化简:根据给定要求得到的原始状态图很可能包含有多余的状态,需要进行状态化简或状态合并。状态化简是建立在状态等价这个概念的基础上的。

(3)状态编码、并画出编码形式的状态图及状态表:在得到简化的状态图后,要对每一个状态指定1个二进制代码,这就是状态编码(或称状态分配)。

(4)选择触发器的类型及个数:

(5)求电路的输出方程及各触发器的驱动方程:根据编码后的状态表及触发器的驱动表可求得电路的输出方程和各触发器的驱动方程。

(6)画逻辑电路,并检查自启动能力。

2.用MSI中规模时序逻辑器件构成时序逻辑电路

用中规模时序逻辑器件构成的时序功能电路主要是指用集成计数器构成任意进制计数器。构成任意进制计数器的方法有两种:一种是置数法,另一种是归零法。