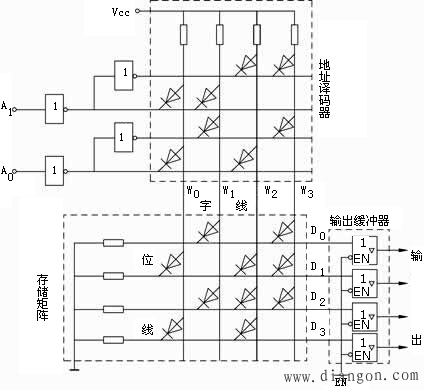

下面以图1所示的二极管ROM存储器电路说明ROM的工作原理。

|

| 图1 ROM的工作原理 |

由图1可知,该二极管ROM包含两个主要部分:由二极管组成的地址译码器和存储矩阵。

(1)地址译码器

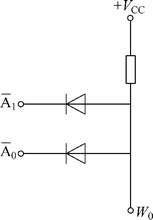

地址译码器是由二极管与门电路构成,包括两个地址代码输入端A0、A1,4个地址输出端W0、W1、W2和W3,每个地址输出端和两个地址代码输入端之间是与逻辑运算关系,如图2所示。

|

| 图2 二极管ROM电路 |

由图1可以得出,地址译码器输出的4个地址与两位地址代码之间的逻辑表达式为

| (1) |

由式(1)可知,地址译码器具有以下特点。

①当输入地址代码A1A0分别为00、01、10、11时,字线W0、W1、W2、W3分别为“1”,即无论A1A0为何种取值时,4条字线中只能有一条为高电平。

②ROM地址译码器的地址输出与其它地址代码输入的全部最小项对应,即地址译码器的输出地址个数等于地址代码的最小项数目,并且一一对应。如两个地址代码A1和A0的全部最小项为![]()

![]() 、

、![]() A0、A1

A0、A1![]() 和A1A0,共4个。因此地址译码器的输出地址也有4个,并一一对应,如图2所示。

和A1A0,共4个。因此地址译码器的输出地址也有4个,并一一对应,如图2所示。

(2)存储矩阵

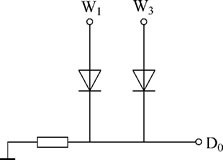

由图3可知,该电路的存储矩阵是由二极管或门电路构成。字线W0~W3是输入,位线D0~D3是输出。输入与输出之间符合或逻辑运算,如图3所示。

|

| 图3 输出与输入之间符合逻辑关系 |

由图1可以得出以下输出逻辑式:

| (2) |

由图3可知,ROM存储矩阵中存储的数据是根据不同需要,在设计和制造时已经完全确定,不能改变。而且信息存入后,即使断开电源,所存的信息也不会消失。

由式(1)和式(2)可以得出,图7-4所示ROM存储器内容及其与地址代码的对应关系列于表1中。

| 表1 图1所示ROM的输出信号真值表 |

| 地 址 代 码 | 地址线(字线) | 数据线(位线) | |||||||

| A1 | A4 | W3 | W2 | W1 | W4 | D3 | D2 | D1 | D4 |

| 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

| 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 |

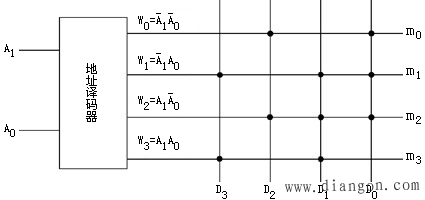

综上所述,图3所示ROM电路中,地址译码器是一个与逻辑阵列,存储矩阵是一个或逻辑阵列。图3可以画成如图4所示的简化电路。有二极管的存储单元用一个黑点表示。这样,就使ROM地址译码器和存储矩阵之间的逻辑关系表达得十分简捷和直观。

|

| 图4 图1的简化画法 |