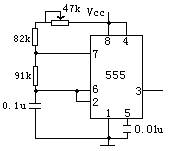

用 555 实现多谐振荡,需要外接电阻R1,R2和电容C。

电路图如下:

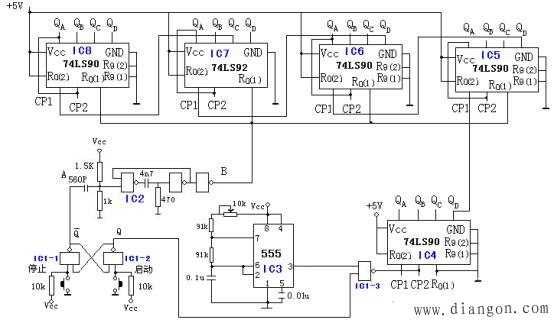

2)分频器电路

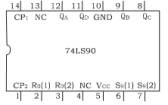

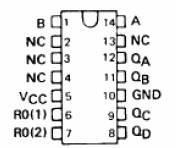

通常,数字钟的晶体振荡器输出频率较高,为了得到 0.1Hz的秒信号输入,需要对振荡器的输出信号进行分频。 须设计一个五进制计数器 ,对频率为 50HZ 的时钟脉冲进行五分频,在输出端 QD 取得周期为 0.1S 的矩形脉冲,作为 时间计数单元的时钟输入。 用集成异步计数器 74LS90 实现,电路图如下:

图2 74ls90引脚图及构成五进制计数器

3)时间计数单元

时间计数单元有时计数、分计数和秒计数等几个部分。 要实现 0.1 秒计数,须设计一个 10 进制计数器;要实现秒计数,须设计一个 60 进制计数器;要实现分计数,须设计一个 10 进制计数器,这里选用 74LS90 实现。

表1 74LS90功能表

|

输 入 |

输 出 |

功 能 | |||||||

|

清 0 |

置 9 |

时 钟 |

QD QC QB QA | ||||||

|

R0(1)、R0(2) |

S9(1)、S9(2) |

CP1 CP2 | |||||||

|

1 |

1 |

0 × |

× 0 |

× × |

0 |

0 |

0 |

0 |

清 0 |

|

0 × |

× 0 |

1 |

1 |

× × |

1 |

0 |

0 |

1 |

置 9 |

|

0 × × 0 |

0 × |

↓ 1 |

QA输出 |

二进制计数 | |||||

|

1 ↓ |

QDQCQB输出 |

五进制计数 | |||||||

|

↓ QA |

QDQCQBQA输出 8421BCD 码 |

十进制计数 | |||||||

|

QD↓ |

QAQDQCQB输出 5421BCD 码 |

十进制计数 | |||||||

|

1 1 |

不 变 |

保 持 | |||||||

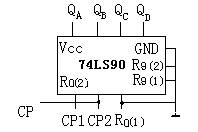

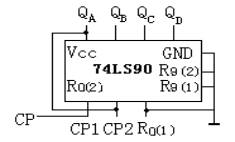

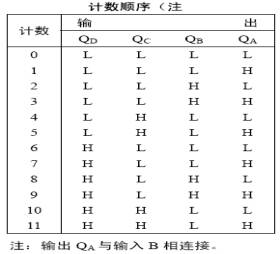

十分之一秒计数器和分计数器是十进制,所以只需要将 74LS90 接成十进制即可。电路图如下:

图4 74LS90构成十进制计数器

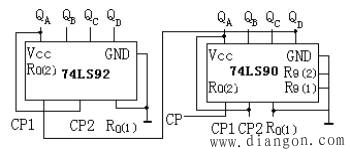

74LS90 是二 -- 五十进制计数器,所以设计一个60进制秒计数器要用两个 74LS90 ,当计数状态一到 01100000 立即清零。但是用90实现六进制时须将QC,QA分别接 R0(1)、R0(2),这样由启动停止电路输出的启动停止秒表工作的信号就无法接到 R0(1)、R0(2)处控制。所以本设计中改用 74LS92 实现 60 进制计数。

12 分频计数器 74LS92 简介

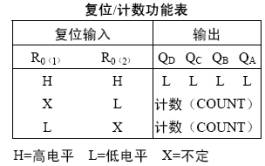

图5 74LS92 引脚图 表2 74Ls92 复位计数功能表

表3 74LS92 计数功能表

74LS92 内部是由 4 个主从触发器和用作除 2 计数器及计数周期长度为除6的3位2进制计数器所用的附加选通所组成。为了利用本计数器的最大计数长度(十二进制),可将 B 输入同 Q A 输出连接,输入计数脉冲可加到输入A上,此时输出如功能表2所示。

所以六十进制计数器电路图如下:

图6 92 及 90 构成六十进制计数器

4) 码驱动及显示单元

计数器实现了对时间的累计以 8421BCD码形式输出,用显示译码电路将计数器的输出数码转换为数码显示器件所需要的输出逻辑和一定的电流。

本设计用的 CD4511是用于驱动共阴LED显示器的BCD-84217段译码器。

(5) 脉冲整形电路 单元

将启动和停止电路输出的不规则脉冲整形为具有一定幅度和一定宽度的脉冲,为计数器提供清零信号。 启动和停止电路单元的按钮按下, 则此电路输出一个持续时间一定的有效信号( 负脉冲 )。在此期间, 即使按钮有几个连续的负脉冲 , 但电路输出仍保持低电平 , 从而将按钮的抖动屏蔽掉。

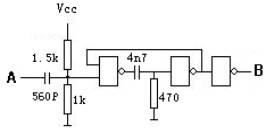

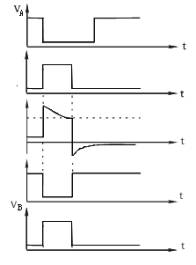

本设计用微分型单稳态触发器实现。 电路图和波形图如下:

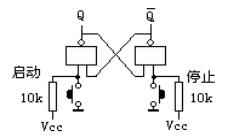

6)启动和停止电路单元

用集成与非门构成的基本 RS 触发器作为 启动和停止秒表工作的电路 。

电路图如下:

图9 RS触发器电路

总电路图如下:

图10 电子秒表总电路图