本文将信息工程领域的计算机软件技术——信息重构技术引入智能变电站二次系统设计中,阐述了动态重构技术应用于智能变电站二次系统的适用性,提出了可用于二次系统的设计理念。

1智能变电站动态重构

1.1系统配置原理

系统重构在开发早期是作为信息工程领域的技术,主要用于修改代码结构和流程设计。随着这项技术的不断发展,其技术不断形成系统,目的在于不改变已有系统功能的情况下,通过修改系统的运行方式来满足需求变化。

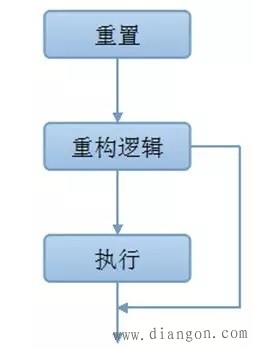

动态重构是指在系统实时运行的过程中对功能进行动态配置。其实现方式如图1所示。

图1动态重构方式

动态重构在现阶段功能实现主要包括软件重构、硬件重构以及二者的协同。软件部分属于软件工程研究领域范畴;硬件重构技术多基于现场可编程门阵列(FPGA)实现,可重构控制模块能够驱动FPGA实现资源的高速功能变换,目前FPGA越来越成为可重构技术的热点;软硬件的协同技术指根据系统功能需求,统筹考虑性能、成本等因素合理配置软硬件功能,可以有效提高效率,节约成本。

1.2基本框架

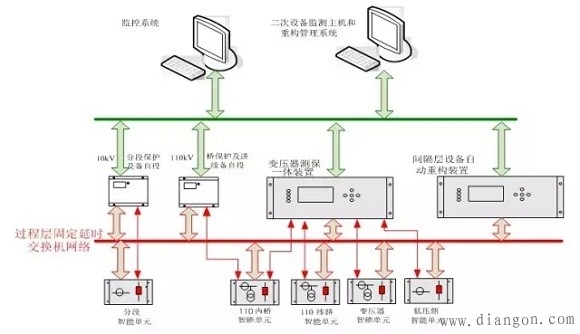

二次监测评估及重构管理系统实现主运行设备与重构设备的监测信息采集、根据规则库评估设备运行状态、匹配重构控制策略、管控主运行设备与重构设备的切换等任务。同时,二次监测评估及重构管理系统的运行状态及监控信息传给站控层监控系统,实现站控层监控系统的一体化信息采集。

动态重构基础按照系统结构分为过程层、间隔层和站控层,在这一点上与智能变电站相配合,所不同之处在于间隔层增加了备用的IED,站控层增加了管控主机。如图2所示。

图2二次系统重构实现架构图

管控主机可以监视全站IED的状态变量,在线评估IED运行状态,而管控主机可以控制和管理全站IED。在某个IED故障时,给予告警并记录信息,同时显示故障IED的历史运行信息,对故障进行分析,并指导运行人员做出判断,这样实现IED重构。

2重构设备

目前的动态重构设备多采用主CPU和FPGA共同组成的多处理器做为硬件平台,通过运行操作系统,完成系统的硬功功能。硬件平台基于嵌入式计算机,通信协议包括MMS、GOOSE、IEEE1588等通信服务,可以满足智能变电站即插即用的要求;软件平台采用操作系统和嵌入式数据库。

2.1软件平台

CPU板的软件包括硬件驱动、系统级平台、通信、应用、人机、测试及自检等几大部分,操作系统选用嵌入式实时系统vxWorks,利用中断机制及任务机制,来协调处理不同功能。硬件驱动部分主要包括与硬件有关的驱动程序及硬件管理程序,包括内存分配、网口驱动、人机接口收发、维护接口驱动、文件系统管理、信号灯、对时驱动等的管理等。

系统软件平台的功能主要包括系统管理、硬件自检、软件校验、时间处理、以及必要的信息打印输出等。

软件系统作为一个平台,组织结构上具有相当的伸缩性、灵活性,因此采用当前主流的、具有多进程/多线程、准实时的嵌入式操作系统。应用软件的结构组成采用了多进程和共享内存数据库,各个进程以共享内存数据库为中心进行数据交互和消息交换,由管理进程进行各个应用进程的协调启动、运行状态监护。

利用共享内存数据库,管理进程程序通过搭配不同的应用进程,可以灵活的实现多种应用系统。增加新的功能,就增加启动一个相应的进程;不需要的功能,只是简单的不启动一个相应的进程;这些都由配置通过管理进程程序来实现,具有很好的开放性、灵活性。一个应用进程的出错,不会影响到整个应用系统的运行,具有良好的可靠性、安全性。

其应用功能主要包括通信处理、重构功能实现、配置参数等管理以及装置的整体校验测试等。

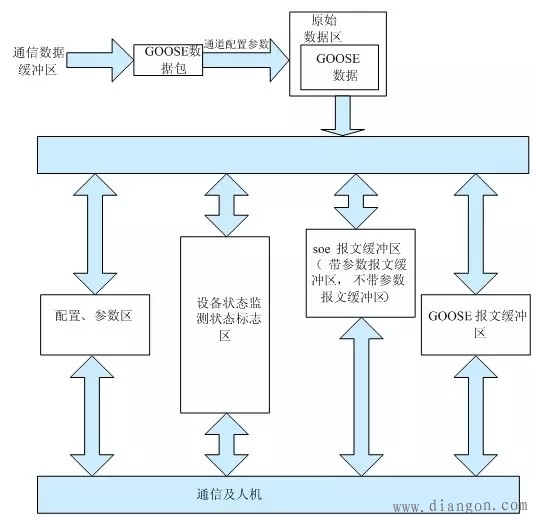

设备数据及信息的流向如图3所示。设备从网络口数据缓冲区读入GOOSE报文,解析后处理成开关量输入,存入“原始数据缓冲区”。配置、参数的修改维护由就地人机或通信完成,存放于“配置、参数区”。

设备根据预设的配置、参数,实现应用功能,由此而产生的设备状态及输入状态的标志等置入“设备状态监测状态标志区”,产生的各种报文置入“soe报文缓冲区”,发出的控制指令置入“GOOSE报文缓冲区”。

通信和人机从各缓冲区中获得所需的数据,实现就地显示、控制或传向其他设备交互信息。

图3数据及信息流

2.2重构硬件设备

目前的重构设备主要由CPU板主板和网络接口板组成。

2.2.1CPU板

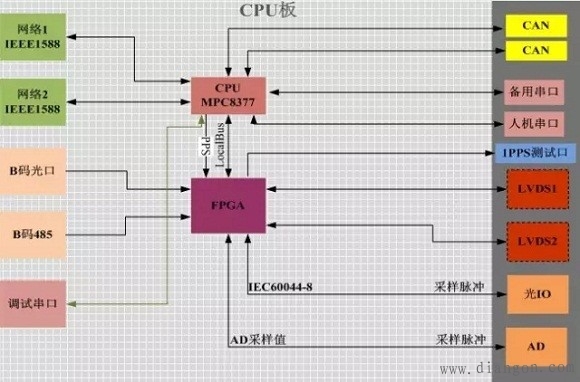

CPU板包括CPU主板和CPU的FPGA板

1)CPU板主板

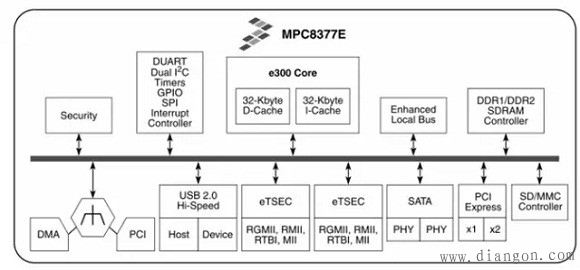

CPU插件的主CPU采用MPC8377E。MPC8377E处理器采用e300core,主频可达667MHz;带MMU,DDR2内存最高400MHz;32位LocalBus,最高133MHz,支持NandFlash启动;32位PCI总线,最高66MHz;2个PCI-E接口;2个SATA接口;2个10/100/1000Mbit的以太网接口;1个USB2.0接口;2个UART;2个I2C;1个SPI。如图4所示。

图4CPU板插件硬件框架

CPU板主变的主要资源如图5所示。

图5MPC8377模块框图

2)CPU板的FPGA板

CPU板的FPGA实现的功能比较复杂,为数据处理的核心部分。

FPGA同时接收左向和右向网络板FPGA的数据,并按照相应的顺序填写到SDRAM中,并使能中断信号,提示CPU可以接收网络数据。

由于SDRAM不能同时读写。当CPU响应FPGA中断接收数据时,将会同时占用FPGA和一片SDRAM的LocalBus,如果此时网络板FPGA有数据包传递进来的话,就只能缓冲到第二块SDRAM。然后发起中断,提示数据到来,CPU将会读取第二块SDRAM,以此类推,由两块SDRAM实现了双口RAM的功能。

由于CPU与FPGA之间只有一个LocalBus接口,当CPU与SDRAM进行数据通信时,LocalBus会被占用,此时CPU无法访问FPGA,最好增加一个SPI接口,CPU可以通过SPI接口适时访问FPGA。

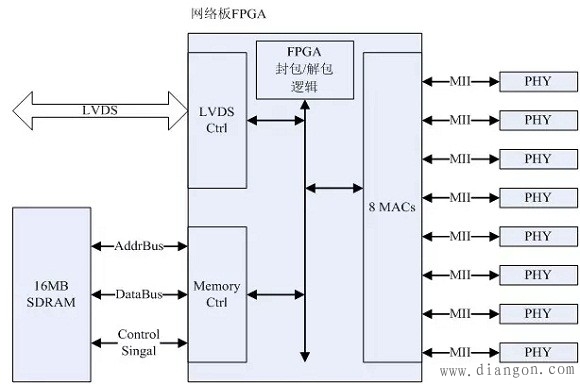

2.2.2网络接口板

每个网络接口板配置8个网络接口。每个以太网口均有link及act指示灯,用于表征各网络接口及接口板的工作状态。通过更换元器件可实现网络的电接口或光接口。网络接口板通过FPGA实现以太网口驱动、网络接口板与CPU板的通信。网络接口板与背板联络,为光纤接口和CPU通信传递信息。网络接口板与CPU板之间采用光纤通信。

网络接口网络板硬件框图如图6所示,主要由以下三部分组成:(1)FPGA模块,主要实现FPGA封包解包逻辑、8个10/100MMACs、LVDS高速总线控制器以及SDRAM存储器控制器。(2)SDRAM模块,主要实现网络数据帧的存储、转发。(3)PHYs模块,包括8个10/100M以太网PHY芯片。PHY芯片建议选RTL8208B,该芯片为8路10/100Base-T/TX和100Base-FXPHY,也可以选择RTC8201或IP101A等芯片。板采用子母板设计方式。

图6网络板FPGA功能模块

2.3FPGA功能设计

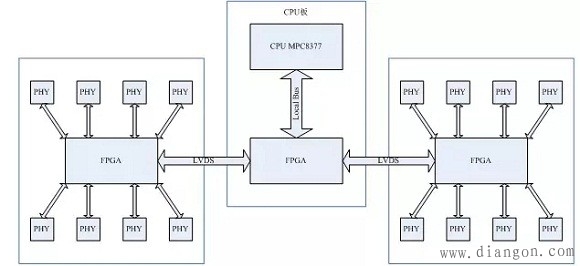

2.3.1系统逻辑

FPGA设计包括CPU板FPGA设计和网络板FPGA设计两部分。网络板的FPGA主要实现扩展网络功能和网络数据的解码功能;CPU板的FPGA主要实现CPU与FPGA之间的数据通信以及与网络板FPGA的交互数据的功能。功能如图7所示。

图7FPGA系统连接图

2.3.2FPGA逻辑功能

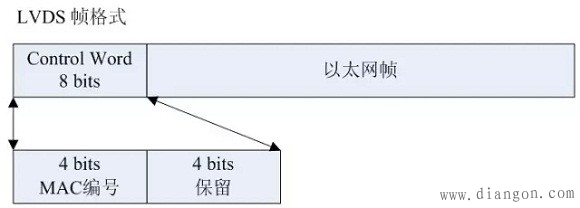

其主要功能是完成8个以太网MAC与串行的高速LVDS总线之间的通信。可以实现8个10/100MMAC与8个PHY芯片进行数据交互。为每一个MAC设计两个帧的缓冲区,每个缓冲区大小为2048字节;同时可以实现LVDS本方案考虑使用LVDS接口实现FPGA之间的互联。FPGA收到网络数据包之后,通过8b/10b编码转换成(至少)1Gbps的网络数据流,将其传输到CPU板的FPGA。

但由于封包解包逻辑8个以太网MAC的数据是并行的,而LVDS总线是串行的,所以还要考虑:LVDS选择性的从8个MAC读取数据传输。其选择MAC的顺序是1至8,而后绕回到1;其选择依据是当前MAC的缓冲区是否有合法的数据帧,如果有则发送,没有则直接跳过。LVDS传输的帧格式如图8所示。

图8LVDS帧格式

结论

本文根据智能变电站二次功能实现的工程设计,研究了智能变电站二次系统动态重构,提出了动态重构功能的硬件及软件解决方案。在研究过程中,以智能变电站二次功能实现的各个环节为基础,研究了智能变电站基于信息共享的二次设备功能软件构造技术及功能软件组件实现技术。

重构技术在智能变电站运行及维护工作中的自愈、自适应、自恢复等方面具有一定优势,为智能变电站二次系统提供了新的手段,增加了二次系统运行的灵活性,有利于推动变电站智能化进程。