寄存器是存放数码的逻辑部件,它必须具备接收和寄存数码的功能。采用任何一种类型的触发器均可构成寄存器。每一个触发器存放一位二进制数或一个逻辑变量,由n个触发器构成的寄存器可存放n位二进制数或n个逻辑变量的值。

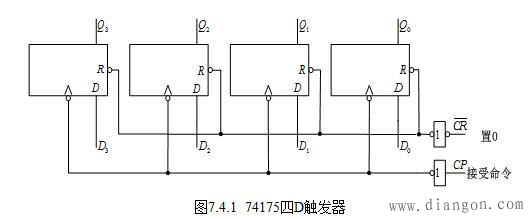

图7.4.1所示为74175四D触发器的逻辑图。当接收命令 (即时钟脉冲CP)到来时,数码便送到寄存器保存起来。由于寄存器中触发器的状态改变是与时钟脉冲CP同步的,故称同步送数方式。

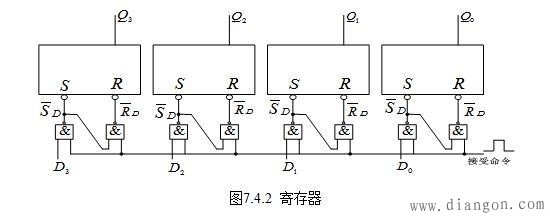

利用触发器的D和D也可以实现送数,达到寄存数码的目的,其连接方式如图7.4.2所示。这种工作方式称为异步送数,寄存器状态改变的时刻与时钟脉冲CP无关。

图7.4.1和图7.4.2中数码的各位是并行送入寄存器的;寄存器寄存的数码也是并行地将数码的各位一齐输出,称为并行输入,并行输出。