来源:本站

导读:目前正在解读《VHDL并行语句结构》的相关信息,《VHDL并行语句结构》是由用户自行发布的知识型内容!下面请观看由(

电工学习网 - www.9pbb.com)用户发布《VHDL并行语句结构》的详细说明。

VHDL并行语结构最具硬件描述语言特色

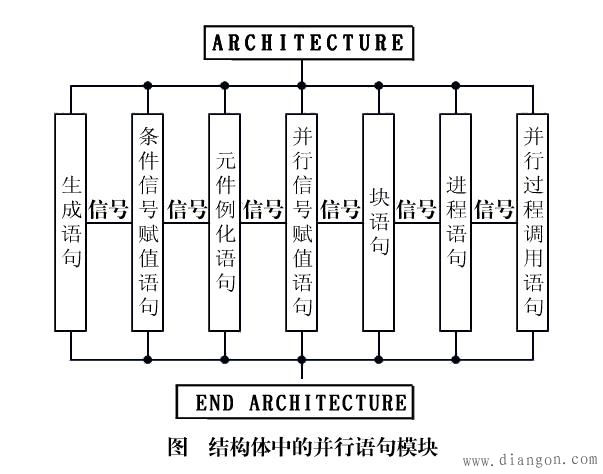

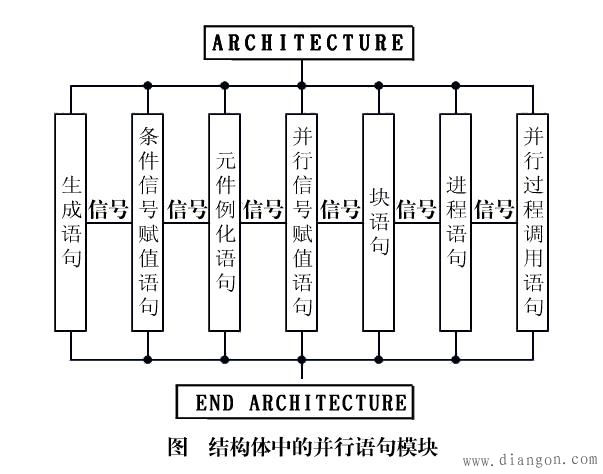

并行语句具有如下多种语句格式:

1、进程语句

2、并行信号赋值语句

3、元件例化语句

以上各并行语句在结构体中是同步执行的,其执行方式与书写顺序无关。并行语句之间可以有信息往来,也可以是互为独立、互不相关、异步运行的(多如时钟情况)。

上图所示的是在一个结构体中各种并行语句运行的示意图。这些语句不必同时存在,在每一语句模块都可以独立异步运行,模块之间并行运行,并通过信号来交换信息。

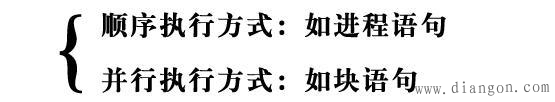

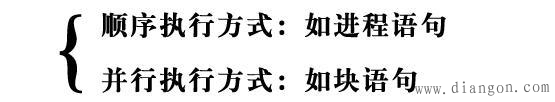

每一并行语句内部的语句运行方式:

VHDL并行语句勾画出了一幅充分表达硬件电路的真实的运行图景。

提醒:《VHDL并行语句结构》最后刷新时间 2023-07-10 03:51:47,本站为公益型个人网站,仅供个人学习和记录信息,不进行任何商业性质的盈利。如果内容、图片资源失效或内容涉及侵权,请反馈至,我们会及时处理。本站只保证内容的可读性,无法保证真实性,《VHDL并行语句结构》该内容的真实性请自行鉴别。