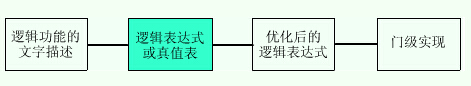

1.由真值表、逻辑方程到门级实现

图1 一种组合电路的设计过程

例1 算术逻辑运算单元(ALU)的设计。

算术逻辑运算单元是许多数字系统的主要部件,其框图如下:

图2 1位ALU

ALU的功能表如下:

表21 ALU的功能表

2.功能分析和函数分解

例2 设计如下图所示的并行补码变换器。

|

|

变换器的输入是原码 S是符号位 B = B3B2B1B0为数值位 输出为相应的补码 F = F3F2F1F0

|

图3 并行补码变换器

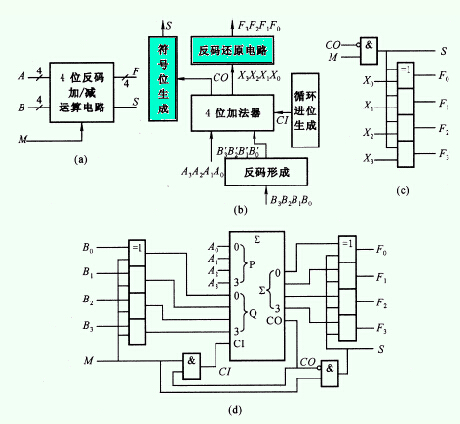

例3 设计如下图所示的二进制加/减运算电路。

| 操作数[A]原 = A3A2A1A0,

[B]原 = B3B2B1B0,是无符号二进制原码。 结果用原码表示, F = F3F2F1F0为数值位, S为符号位, M为加/减控制信号。 |

图4 无符号二进制加/减运算电路

3.改进原电路,实现逻辑功能

图5 加/减运算电路之一

4.积木块化设计

例4 设计如图所示的8位算术比较器,该比较器接受两个无符号二进制数A = a7a6a5a4a3a2a1a0和B = b7b6b5b4b3b2b1b0。当A>B时,输出Z = 1;否则Z = 0。

表4 比较器积木块功能表

图6 比较器积木块

如图6 所示,用8个这样的积木块级联可以构成所需要的8位数值比较器。

例6 设计如图7 所示的4位并行乘法器

|

两个4位二进制数相乘的过程如下:

|

|

图7 4位乘法器的一种电路

图8 用积木块构成的乘法器

5.逻辑验证和逻辑模拟

要使设计结果必须符合设计要求,必须对设计结果进行检查和核对,这就是逻辑验证。

基于表格的事件驱动法,用若干张表格来描述逻辑图。

图9 2选1MUX逻辑图 |

表5 引线表和元件表 |

图10 队列变化

表6 电平变化表